2 频率源方案设计

这一章节将根据实际项目的需求分析各个方案的可行性,结合各个组成模块的原理介绍和实现方式,确定最终的方案选择并给出原理框架图。

2.1 系统指标分析

根据项目最终需要的W波段的频率综合器,本课题的X波段的频率源作为其构成的一部分,设计指标时必须从整体的需求考虑。

W波段频率源指标要求:

频率范围: 92.5~96.5GHz

频率步进: 1MHz

跳频时间: 1ms

相位噪声: 80dBc/Hz@10kHz

我们一般通过混频或者倍频的方式将低波段的信号源变频为高波段的信号源。而对于毫米波段的信号,若采用混频方式则仍需要一个较高频段的中频信号,结构会相对复杂。所以一般我们采用倍频的方式,那么这里首先需要确定一个重要微波器件,即W波段的倍频器。因为在设计方案的时候除了需要考虑理论上的可行性,还要确定是否有市售的器件可购得。在这一次的设计中,最初采用的是内混频获得12GHz的信号再通过八倍频到96GHz,而后来发现八倍频器很难购得,且谐波抑制度较低。经查询后可知比较普遍的是优尔倍频器,所以需要获得一个16GHz的信号。而在VCO芯片的查询中发现并没有合适这个频段的,所以不能直接锁相至16GHz的信号,那么同样的我们有两种解决方式,倍频或者混频得到它。此外为了获得可控的步进频信号,采用设计中应用最广泛的DDS激励PLL结构[7] [9]。

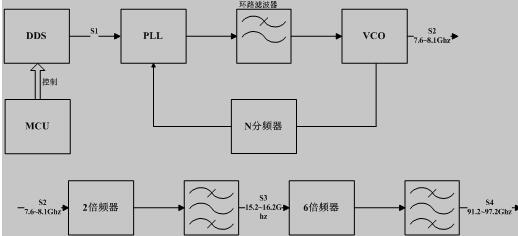

采用倍频方式,那么整体的结构便是8GHz信号先通过2倍频再6倍频至W波段,其结构框图如图2.1所示:

图2.1 倍频方案框图

若采用混频方式,结构框图如图2.2所示,通过一路锁相环路输出一个点频信号作为中频信号,另一路由DDS激励输出扫频源,两个信号混频之后再6倍频至W波段。 X波段频率综合器+文献综述+PCB电路图(3):http://www.youerw.com/tongxin/lunwen_29287.html